| Tần số kích thích 50Hz, 400Hz và 2.6kHz |  |

| Độ phân giải: 10 bit, 12 bit, 14 bit | |

| Tốc độ theo dõi cao | |

| Đầu vào không tiêu chuẩn có thể điều chỉnh thông qua điện trở bên ngoài hoặc điều chỉnh tại đầu vào sản phẩm | |

| Điện áp DC đầu ra tỷ lệ thuận với vận tốc góc | |

| Tương thích với dòng SDC1700 của công ty AD của Mỹ |

sự chuyển đổi. | Nguồn hoạt động là ± 15V và nguồn + 5V DC. Có hai loại |

tín hiệu đầu ra: tín hiệu tham chiếu và đồng bộ ba dòng (bộ chuyển đổi SDC) | |

hoặc bộ phân giải bốn dòng và tín hiệu tham chiếu (bộ chuyển đổi RDC); đầu ra | |

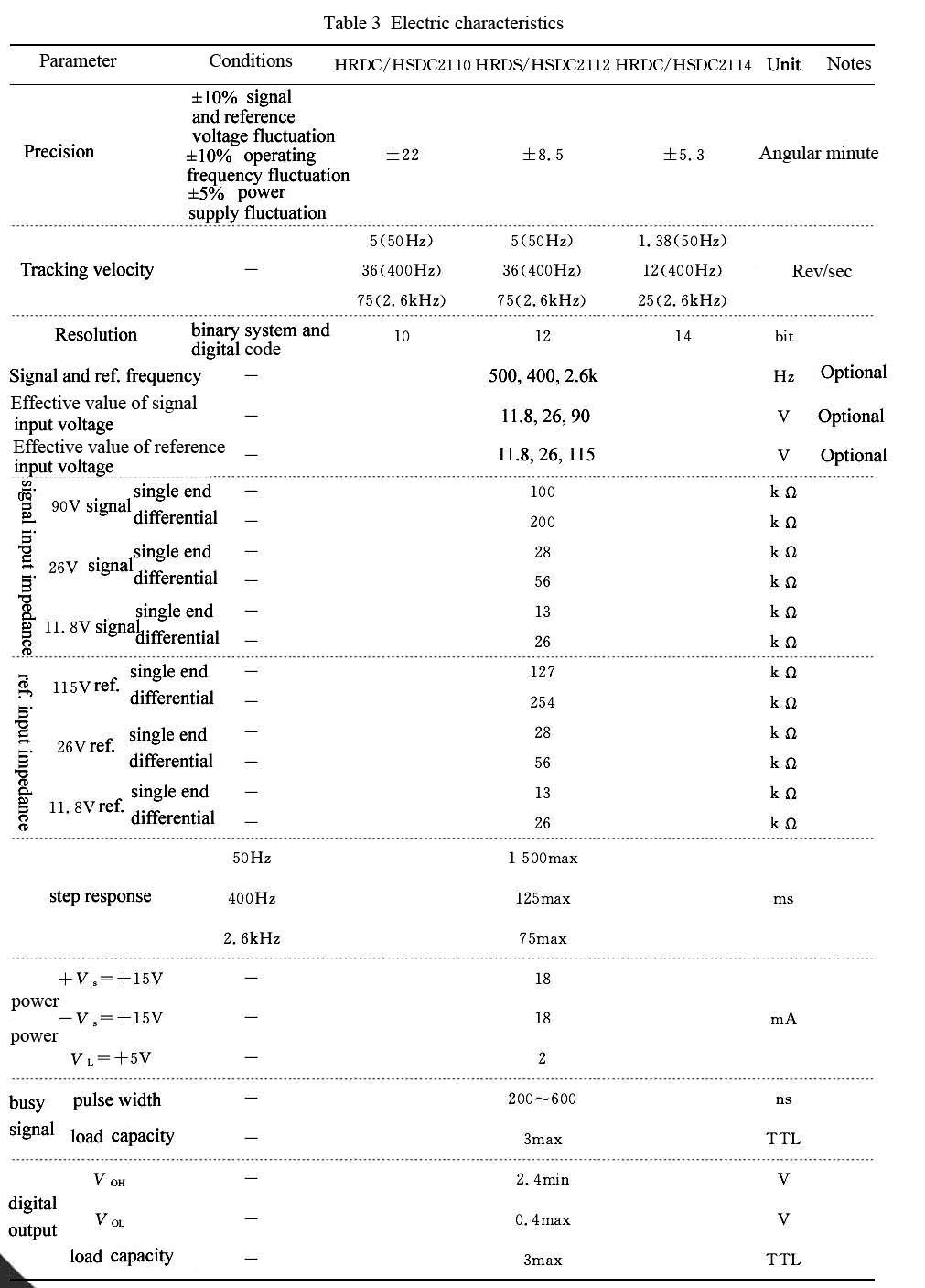

là các mã số song song của hệ nhị phân. | 4 Hiệu suất điện (Bảng 2, Bảng 3) của Đồng bộ đến |

Bộ chuyển đổi kỹ thuật số hoặc Bộ phân giải thành Bộ chuyển đổi kỹ thuật số (HSDC / HRDC211 | |

Hàng loạt) | |

Bảng 2 Các điều kiện định mức và điều kiện vận hành khuyến nghị | |

Giá thầu tối đa tuyệt đối giá trị đánh giá | |

Điện áp cung cấp Vs: ± 17,5V |

| Giá trị hiệu dụng của điện áp tham chiếu VRef: 11,8V, 26V, 115V Giá trị hiệu dụng của điện áp tham chiếu V1 *: 11,8V, 26V, 90V |  Tần số tham chiếu f *: 50Hz, 400Hz, 2.6kHz |

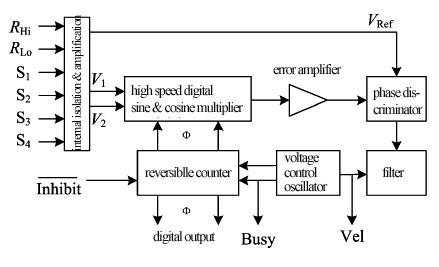

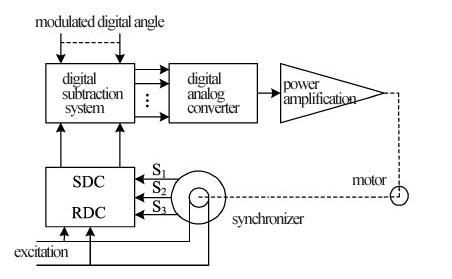

Trong đó, θ là góc đầu vào tương tự Tín hiệu trực giao được nhân với góc kỹ thuật số nhị phân φ trong Tín hiệu trực giao được nhân với góc kỹ thuật số nhị phân φ trong | bộ đếm thuận nghịch bên trong trong hệ số nhân hàm sin-côsin và |

θ-φ ≠ 0, bộ dao động điều khiển điện áp sẽ xuất ra xung để thay đổi | dữ liệu trong bộ đếm có thể đảo ngược, cho đến khi θ-φ trở thành 0 trong |

|  |

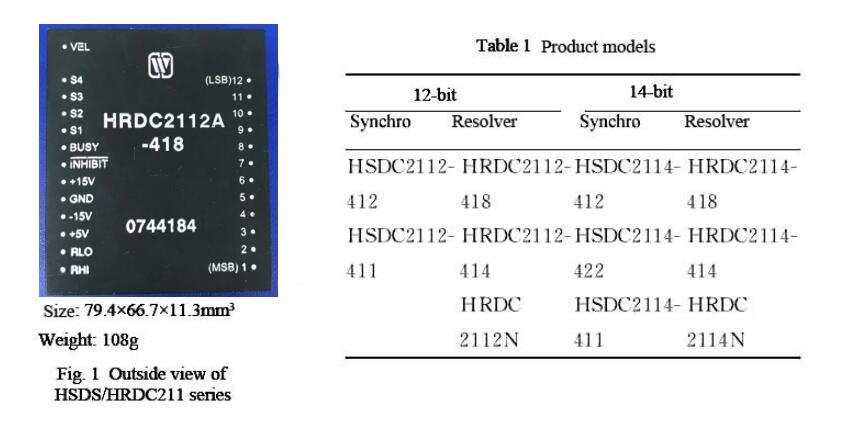

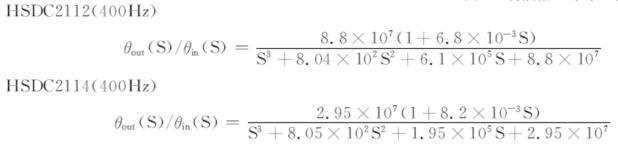

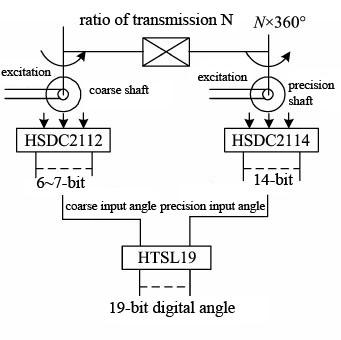

| độ chính xác của bộ chuyển đổi, trong quá trình này, bộ chuyển đổi theo dõi thay đổi góc đầu vào θ mọi lúc. Về nguyên lý làm việc, xem Hình. | 2. Hàm truyền: sau đây là các tham số cho chức năng truyền của HSDC2112 và HSDC2114 (400Hz), đối với các kiểu máy khác, vui lòng liên hệ với nhà sản xuất trực tiếp. Hình 2 Sơ đồ khối cho nguyên tắc hoạt động của bộ chuyển đổi |

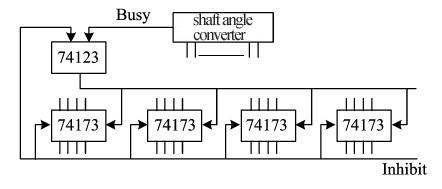

Có hai phương pháp để đọc dữ liệu hợp lệ của bộ chuyển đổi như sau: | Phương pháp ức chế (đọc đồng bộ): | Đặt Cấm thành logic “0”, tại thời điểm này, bộ chuyển đổi sẽ ngừng theo dõi. Chờ | 1μs cho đến khi dữ liệu đầu ra ổn định, đọc dữ liệu, dữ liệu đọc là | hợp lệ tại thời điểm này (1μs đã bị trì hoãn). Đặt thành logic “1”, tại thời điểm này, bộ chuyển đổi sẽ bắt đầu theo dõi lại để sẵn sàng đọc dữ liệu hợp lệ tiếp theo. | Phương thức bận (đọc không đồng bộ): Ức chế |

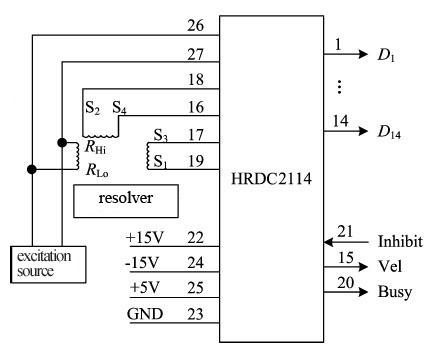

1 | D1 | Trong chế độ đọc không đồng bộ, | 15 | được đặt thành logic “1” hoặc bỏ trống, nếu vòng lặp nội bộ luôn ổn định | trạng thái hoặc nếu dữ liệu đầu ra là hợp lệ sẽ được xác định thông qua |

2 | D2 | trạng thái của tín hiệu bận rộn Bận. Khi tín hiệu Bận ở mức cao, nó | 16 | S4 | cho biết dữ liệu đang được chuyển đổi và dữ liệu tại thời điểm này là |

3 | D3 | không ổn định và không hợp lệ; khi tín hiệu Bận ở mức thấp, nó cho biết | 17 | S3 | chuyển đổi dữ liệu đã hoàn tất và dữ liệu tại thời điểm này ổn định |

4 | D4 | và hợp lệ. Trong chế độ đọc không đồng bộ, đầu ra Busy là dòng xung của | 18 | S2 | Mức TTL, độ rộng giữa có liên quan đến tốc độ quay. Tham khảo |

5 | D5 | Biểu đồ trình tự thời gian của quá trình truyền dữ liệu Hình 3. | 19 | S1 | Hình 3 Trình tự thời gian truyền dữ liệu |

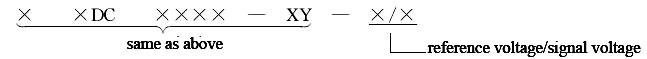

6 | D6 | (2) Phương pháp suy giảm của tín hiệu đầu vào | 20 | Nếu trình đồng bộ hóa hoặc trình phân giải mà người dùng đã sử dụng không phải là tiêu chuẩn, để | làm cho điện áp tín hiệu đầu vào và điện áp kích thích đầu vào phù hợp với |

7 | D7 | giá trị danh nghĩa của bộ chuyển đổi, người dùng có thể áp dụng phương pháp | 21 |

| điện trở suy giảm bên ngoài được kết nối trong chuỗi, tức là cho mỗi 1V |

8 | D8 | vượt quá giá trị danh nghĩa, kết nối điện trở 1,1kΩ nối tiếp tại | 22 | thiết bị đầu cuối đầu vào tương ứng. Khi sử dụng bộ chuyển đổi, loạt | Điện trở ở mỗi đầu nối phải được lựa chọn và trang bị chính xác, |

9 | D9 | và vật liệu kháng của cùng một lô phải được sử dụng để đảm bảo | 23 | độ chính xác chuyển đổi của bộ chuyển đổi trong nhiệt độ rộng | phạm vi, cứ 0,1% thì lỗi khớp của điện trở loạt sẽ |

10 | tạo ra lỗi chuyển đổi góc 1,7 phút. | Khuyến cáo của nhà sản xuất là nên thông báo cho | 24 | nhà sản xuất để tùy chỉnh bộ phân giải hoặc đồng bộ hóa không tiêu chuẩn như | theo các tham số bắt buộc khi người dùng sử dụng chúng. |

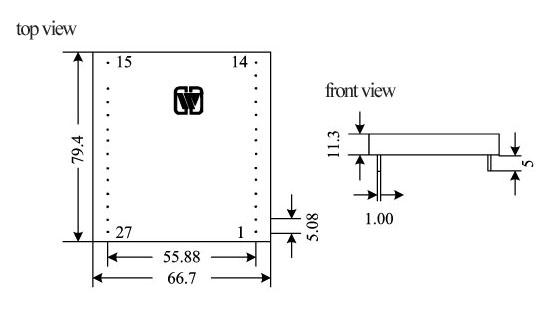

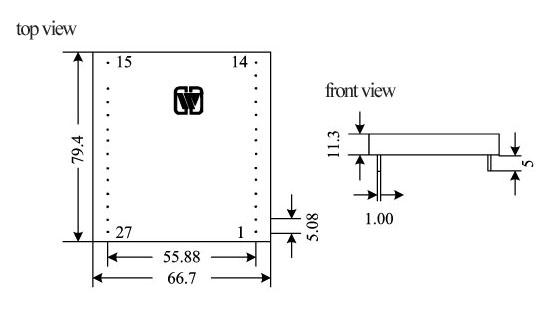

11 | 6 Đường cong MTBF (Hình 4) của Bộ chuyển đổi đồng bộ sang kỹ thuật số hoặc Bộ phân giải thành bộ chuyển đổi kỹ thuật số (Sê-ri HSDC / HRDC211) | Ký hiệu 7 chân (Hình 5, Bảng 4) của bộ chuyển đổi Đồng bộ sang kỹ thuật số hoặc Bộ phân giải thành bộ chuyển đổi kỹ thuật số (Sê-ri HSDC / HRDC211) | 25 | Hình 4 Đường cong nhiệt độ MTBF | (Lưu ý: theo GJB / Z299B-98, dự kiến tình trạng mặt đất tốt) |

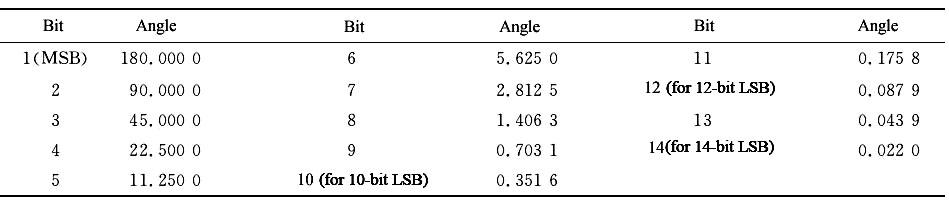

12 | Ghi chú: | ① cấu trúc trên phù hợp với HRDC2114 | 26 | ② cho SDC, không có chân S4 | ③ cho thiết bị 12-bit, không có chân 13 và 14, cho thiết bị 10-bit, không có chân 11, 12, 13 và 14. |

13 | Hình 5 Ký hiệu chân (Hình trên) | Bảng 4 Ký hiệu chân | 27 | Ghim | Biểu tượng |

14 | Hàm số | Ghim |

| Đầu vào tín hiệu Đầu ra kỹ thuật số 6bit 6 Bận Đầu vào tín hiệu bận |  |

| Ngõ ra số 7 |

| -15V |  -15V cung cấp điện |

D11 |

|  |

| + Nguồn điện 5V | D12 |

X

X