| Chuyển đổi cách ly vi sai bên trong |  |

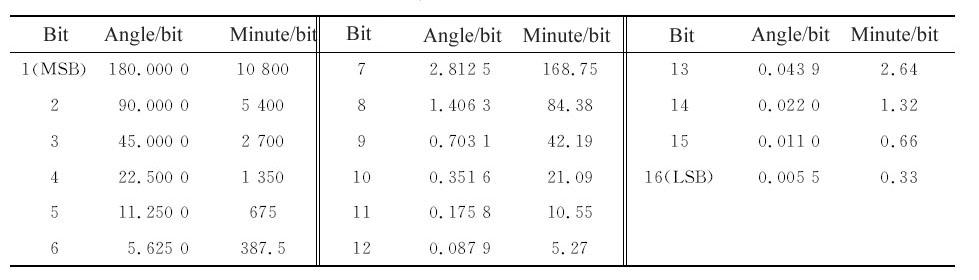

| Độ phân giải 16-bit | |

| Độ chính xác: 2 phút góc | |

| Đầu ra chốt ba trạng thái | |

| Tốc độ theo dõi liên tục cao | |

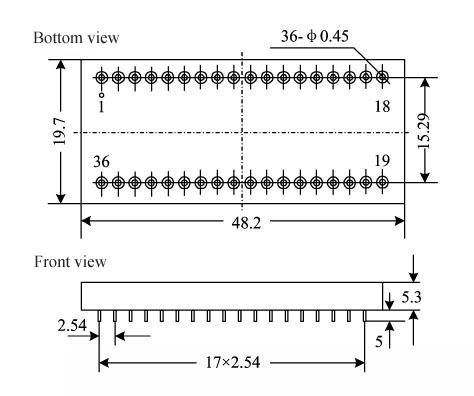

| Gói DDIP kín bằng kim loại chống sương mù 36 dây | |

| Pin-To-Pin tương thích với Model SDC14560 của công ty DDC |

| thiết bị chuyển đổi tích hợp để theo dõi liên tục được thiết kế trên | nguyên lý của mô hình II servo. Dòng sản phẩm này được thiết kế và |

| được sản xuất bằng quy trình MCM, các phần tử cốt lõi sử dụng chip đặc biệt | |

| được phát triển độc lập bởi viện của chúng tôi. Sự sắp xếp pin là | |

| tương thích với các sản phẩm dòng SDC14560 của công ty DDC của Mỹ, 16-bit | |

| Đầu ra chốt dữ liệu mã nhị phân tự nhiên song song, hoàn toàn DIP 36 dòng | |

| gói kim loại kín, có ưu điểm là độ chính xác cao, nhỏ | |

| khối lượng, tiêu thụ điện năng thấp, trọng lượng nhẹ và độ tin cậy cao, v.v., | và có thể được sử dụng rộng rãi trong các vũ khí chiến lược và chiến thuật quan trọng như |

| máy bay, tàu hải quân, pháo, tên lửa, radar, xe tăng, v.v. | |

| 4. Hiệu suất điện (Bảng 1, Bảng 2) | |

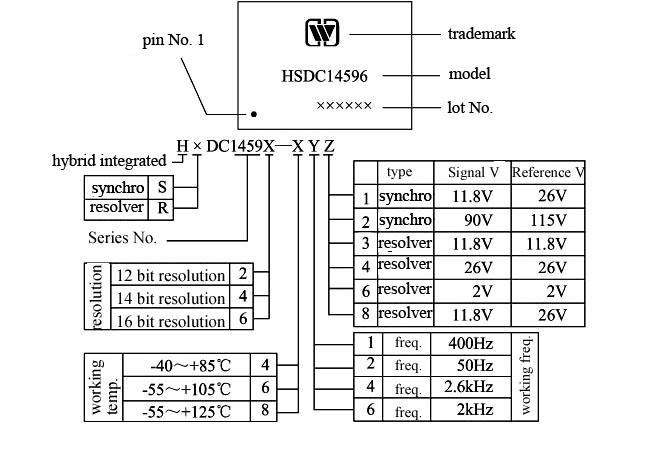

| Đồng bộ với Bộ chuyển đổi kỹ thuật số hoặc Bộ phân giải thành Bộ chuyển đổi kỹ thuật số (Sê-ri HSDC / HRDC1459) | |

| Bảng 1 Các điều kiện định mức và điều kiện vận hành khuyến nghị | |

| Giá thầu tối đa tuyệt đối giá trị đánh giá |

| Điện áp tín hiệu V1: giá trị định mức ± 20% | Điện áp tham chiếu VRef: giá trị danh định ± 20% | Tần số hoạt động f: giá trị định mức ± 20% | |

| Nhiệt độ bảo quản Tstg: -65 ~ 150 ℃ | Điều kiện hoạt động được đề xuất | ||

| Điện áp cung cấp logic VL: 5 ± 0,5V | Điện áp cung cấp Vs: 15 ± 0,75V | ||

| Điện áp tín hiệu V1: giá trị định mức ± 10% | Điện áp tham chiếu VRef: giá trị danh định ± 20% | Tần số hoạt động f: giá trị định mức ± 20% | — |

| Phạm vi nhiệt độ hoạt động (TA): -55 ℃ ~ 125 ℃ | Lưu ý: * cho biết nó có thể được tùy chỉnh theo yêu cầu của người dùng. | Bảng 2 Đặc tính điện | Tham số |

| Điều kiện | — | Dòng HSDC14569 | (VS u003d 15V, VL u003d + 5V) |

| Tiêu chuẩn quân sự (Q / HW20725-2006) | — | 2V | Tối thiểu. |

| Tối đa | — | Nghị quyết | Hệ thống nhị phân mã kỹ thuật số song song |

| 16 bit | — | 2V | Sự chính xác |

| ± 10% điện áp tín hiệu, điện áp tham chiếu và phạm vi dao động của tần số hoạt động | — | -2 phút góc | +2 phút góc |

| Dải tần số tham chiếu | — | 50Hz | 2600Hz |

| Dải điện áp tham chiếu | — | 115V | Trở kháng đầu vào tham chiếu |

4,4kΩ 4,4kΩ | — | 0 | 129,2 kΩ |

Dải điện áp tín hiệu Dải điện áp tín hiệu | — | 0 | 90V |

Trở kháng đầu vào tín hiệu Trở kháng đầu vào tín hiệu | — | 0 | 4,4kΩ |

| 102,2 kΩ | — | Chuyển pha tín hiệu / tham chiếu | —70 ° |

| + 70 ° | — | Mức logic đầu vào | Logic “1” ≥3.3V |

| Logic “0” ≤0,8V | — | đầu vào | 0,8V |

| đầu vào | — | 0,8V | |

| đầu vào | — | — | 0,8V |

| Mức logic đầu ra | — | — | Logic “1” ≥3.3V |

| Logic “0” ≤0,8V | — | — | Đầu ra mã góc kỹ thuật số |

| Logic “1” ≥3.3V | — | — | Logic “0” ≤0,8V |

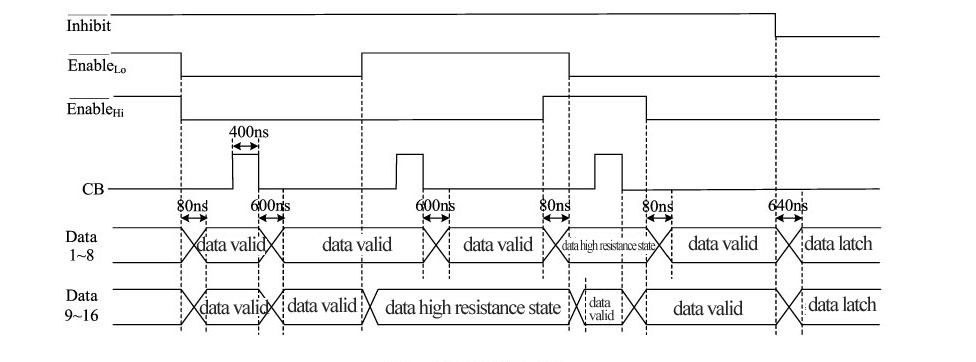

| Chuyển đổi đầu ra tín hiệu bận (CB) | — | 200ns | 600ns |

| Đầu ra bit phát hiện lỗi | Logic “0” chỉ ra lỗi | — | Công suất tải |

| 3TTL | Theo dõi tốc độ | ||

| 2,5rps | Gia tốc không đổi | ||

| + 10V Hiện hành VS u003d + 15V 10mA |  VS u003d —15V |

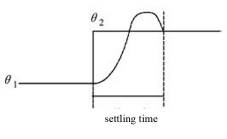

tốc độ. Quá trình dao động của góc kỹ thuật số đầu ra được thể hiện trong

tốc độ. Quá trình dao động của góc kỹ thuật số đầu ra được thể hiện trong 6. Nguyên tắc hoạt động (Hình 3)

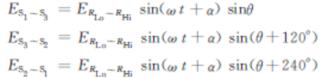

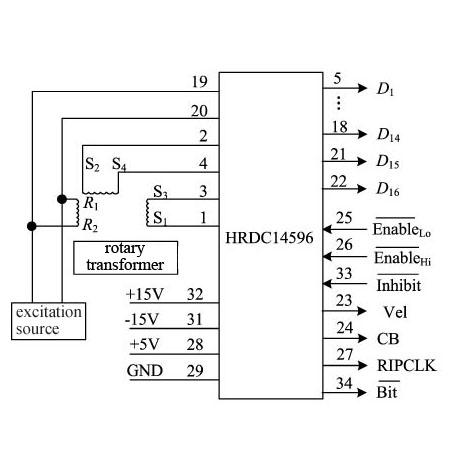

6. Nguyên tắc hoạt động (Hình 3)| Đồng bộ với Bộ chuyển đổi kỹ thuật số hoặc Bộ phân giải thành Bộ chuyển đổi kỹ thuật số (Sê-ri HSDC / HRDC1459) Tín hiệu đầu vào của bộ đồng bộ hóa (hoặc bộ phân giải) được chuyển đổi thành tín hiệu trực giao thông qua cách ly vi phân bên trong: | |

Vcos u003d KE0sin (ωt + α) cosθ (cos)ofTrong đó, θ là góc đầu vào tương tự. Hình 2 Đường cong của phản ứng bước | Hai tín hiệu này và góc kỹ thuật số φ của bộ đếm thuận nghịch bên trongof được nhân lên theo cấp số nhân của các hàm Sine và Cosine và được lỗi đã được xử lý: |

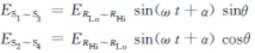

| khuếch đại, phân biệt pha và lọc tích hợp, nếu | θ-φ ≠ 0, bộ dao động điều khiển điện áp sẽ xuất ra các xung, và | đếm ngược có thể đảo ngược, cho đến khi θ-φ trở thành 0 trong độ chính xác của | trình chuyển đổi, trong quá trình này, chuyển đổi theo dõi sự thay đổi của | góc đầu vào mọi lúc. | Phương pháp đọc: |

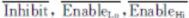

| 1 | S1 | Có hai phương pháp sau để truyền dữ liệu: | 25 |  | (1) Phương pháp ức chế: |

| 2 | S2 | Sau 640ns | 26 |  | mức logic thấp, dữ liệu đầu ra hợp lệ và bộ chuyển đổi nhận ra việc truyền dữ liệu qua |

| 3 | S3 | và | 27 | . Sau khi phát hành In ức chế, hệ thống sẽ tự động tạo ra một xung có độ rộng bằng xung bận để cập nhật dữ liệu. | (2) Chế độ bán thân: |

| 4 | S4 | Tại cạnh lên của xung Busy, bộ đếm có thể đảo ngược ba trạng thái sẽ đếm; ở cạnh giảm dần của xung Busy, bên trong nó tạo ra xung chốt có độ rộng bằng xung Busy để cập nhật dữ liệu của chốt ba trạng thái, chuỗi thời gian truyền dữ liệu được thể hiện trong Hình 4, nói cách khác, sau 600ns của mức logic Busy thấp, việc truyền dữ liệu ổn định là hợp lệ. Trong chế độ đọc không đồng bộ, đầu ra Busy là dòng xung cấp CMOS. Chiều rộng của mức cao và thấp của nó phụ thuộc vào tần số hoạt động và tốc độ quay của thiết bị đã chọn. | 28 | VL | Hình 4 Trình tự thời gian truyền dữ liệu |

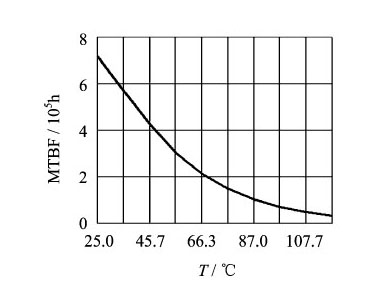

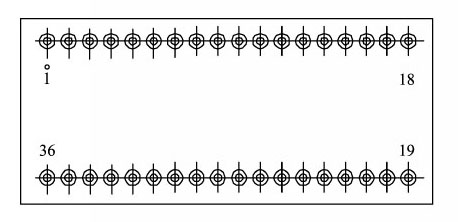

| 7. Đường cong MTBF (Hình 5) | Đồng bộ với Bộ chuyển đổi kỹ thuật số hoặc Bộ phân giải thành Bộ chuyển đổi kỹ thuật số (Sê-ri HSDC / HRDC1459) | Hình 5 Đường cong nhiệt độ MTBF | 29 | 8.Pin chỉ định (Hình 6, Bảng 3) | Đồng bộ với Bộ chuyển đổi kỹ thuật số hoặc Bộ phân giải thành Bộ chuyển đổi kỹ thuật số (Sê-ri HSDC / HRDC1459) |

| 19 | Hình 6 Ký hiệu chân (Hình dưới) | (Lưu ý: theo GJB / Z299B-98, dự kiến tình trạng mặt đất tốt) | 30 | NC | Bảng 3 Ký hiệu chân |

| 20 | RL | Ghim | 31 | Biểu tượng | Nghĩa |

| 21 | Ghim | Biểu tượng | 32 | VS | Nghĩa |

| 22 | Đầu vào bộ phân giải S1 (hoặc đầu vào đồng bộ S1) | Điều khiển kỹ thuật số Enabled 8 bit thấp hơn | 33 | Đầu vào bộ phân giải S2 (hoặc đầu vào đồng bộ hóa S2) | Điều khiển kỹ thuật số Enabled 8 bit cao hơn |

| 23 | Đầu vào bộ phân giải S3 (hoặc đầu vào đồng bộ hóa S3) | RIPCLK | 34 | Ngõ ra tín hiệu 0-bit | Đầu vào bộ phân giải S4 (không kết nối) |

| 24 | CB | Nguồn điện + 5V | 5 月 18 日 | NC | D1-D14 |

| Đầu ra kỹ thuật số 1 (MSB) -14 | GND |

| Đất | RHi |

| Đầu vào tín hiệu tham chiếu cao cấp | Không có kết nối |

| RL | Kết thúc thấp của đầu vào tín hiệu tham chiếu |

-VS

-VS -15V cung cấp điện

-15V cung cấp điện

D15 Đầu ra kỹ thuật số 15

Đầu ra kỹ thuật số 15 ).

).

+ Nguồn điện 15V

D16

Đầu ra kỹ thuật số 16 (LSB)

Ức chế

Đầu vào tín hiệu tĩnh

Vel

S1, S2, S3, S4

S1, S2, S3, S4

Kết thúc thấp của đầu vào tín hiệu tham chiếuofThấp hơn | Đầu vào tín hiệu cho phép chữ số 8 bit, chân này là chân đầu vào logic củaofkiểm soát định vị dữ liệu, chức năng của nó là thực hiện kiểm soát ba trạng thái |

|  |

| bên ngoài trên dữ liệu đầu ra 8 bit thấp hơn của bộ chuyển đổi. Mức độ thấp là | hợp lệ, dữ liệu đầu ra 8 bit thấp hơn của bộ chuyển đổi chiếm dữ liệu |

trạng thái kháng, và thiết bị không chiếm bus dữ liệu. Cho phépvà thời gian trễ phát hành là 600ns (tối đa). | cao hơn | Đầu vào tín hiệu cho phép chữ số 8 bit, chân này là chân đầu vào logic của | kiểm soát định vị dữ liệu, chức năng của nó là thực hiện kiểm soát ba trạng thái | bên ngoài trên dữ liệu đầu ra 8 bit cao hơn của bộ chuyển đổi. Cấp thấp | là hợp lệ, dữ liệu đầu ra 8 bit cao hơn của bộ chuyển đổi chiếmxe buýt dữ liệu; Ở mức cao, chân của dữ liệu đầu ra 8 bit cao hơn ở mức cao | trạng thái kháng, và thiết bị không chiếm bus dữ liệu. Cho phép | và thời gian trễ phát hành là 600ns (tối đa). | Ngăn cản tĩnh |

đầu vào tín hiệu, chân này là chân đầu vào của logic điều khiển, chức năng của nó | là xuất dữ liệu ra bên ngoài cho bộ chuyển đổi để nhận ra tùy chọn | Nichốt hoặc bỏ qua kiểm soát. Ở cấp độ cao, dữ liệu đầu ra của | bộ chuyển đổi đầu ra trực tiếp mà không cần chốt; ở mức thấp, đầu ra | dữ liệu của trình chuyển đổi được chốt, dữ liệu không được cập nhật, nhưngvòng lặp nội bộ không bị gián đoạn và theo dõi đang hoạt động tất cả | thời gian, Inhib có kết nối điện trở kéo lên bên trong. Sau 600ns (tối đa) độ trễ của | Au cạnh giảm dần của tín hiệu tĩnh, dữ liệu trở nên ổn định (cho dù | thiết bị chiếm bus dữ liệu, tức là khi nào nó xuất ra dữ liệu phụ thuộcvề trạng thái của | vàĐầu ra tín hiệu “Bận” CB, tín hiệu này cho biết mã nhị phân |

X

X