| Hệ thống 2 tốc độ hoàn chỉnh |  |

| Tỷ lệ tốc độ có thể lập trình trong kênh thô / mịn | |

| 1: 8, 1:16, 1:32, 1:64 | |

| Đầu ra kỹ thuật số với chốt 3 trạng thái | |

| Độ phân giải tối đa là 20 bit | |

| Độ chính xác tối đa là 5 Arcsec |

| chứa đồng bộ hóa hai chiều thô / mịn tới bộ chuyển đổi kỹ thuật số hoặc bộ phân giải thành |

|

| bộ chuyển đổi kỹ thuật số và sửa lỗi mạch logic được yêu cầu bởi hai |

Tỷ lệ tốc độ của sự kết hợp thô / mịn của các sản phẩm Dòng HTS20 là | 1: 8, 1:16, 1:32, 1: 64 , tỷ lệ tốc độ cần thiết có thể đạt được bằng | chương trình bên ngoài. Nó là thuận tiện để sử dụng. Hai chiều đầu vào thô / mịn tín hiệu là tín hiệu của bộ phân giải đồng bộ ba dây hoặc bốn dây. Đầu ra tự nhiên của bộ chuyển đổi SDC / RDC 2 tốc độ lập trình HTS20 | mã nhị phân song song. Tối đa lên đến 20bit. Họ có 3 trạng thái | chốt. | |

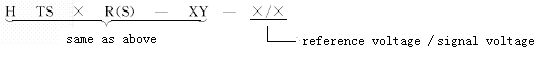

4 THÔNG SỐ KỸ THUẬT của Bộ chuyển đổi đồng bộ sang kỹ thuật số hoặc | Bộ phân giải thành Bộ chuyển đổi kỹ thuật số Sê-ri HTS20 SDC / RDC 2 tốc độ có thể lập trình | ||||

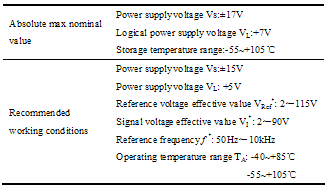

Người chuyển đổi (Tab 2, Tab 3) | Bảng 2 Các điều kiện danh nghĩa và điều kiện vận hành khuyến nghị * có nghĩa là nó có thể được thực hiện để đặt hàng. Bảng 3 Đặc tính điện Đặc trưng Điều kiện | - - - - | 17 18 19 20 | HTS20R / HTS20S | |

Tiêu chuẩn quân sự kinh doanh | (Q / HW30925-2006) Các đơn vị Bình luận Min Max | - - - - | 40 20 10 5 | Nghị quyết | |

(tùy chọn điều khiển bởi SC1, SC2) Tốc độ 1: 8 1:16 | 1:32 - - - | - 50 2 2 | 36 1:64 chút 90 | Độ chính xác (0 ° ~ 360 °) Hz V V | |

|  |

10k 115 | |

,

, Bộ phân giải thành Bộ chuyển đổi kỹ thuật số Sê-ri HTS20 SDC / RDC 2 tốc độ có thể lập trình

Bộ phân giải thành Bộ chuyển đổi kỹ thuật số Sê-ri HTS20 SDC / RDC 2 tốc độ có thể lập trình Bộ chuyển đổi (Hình 2, Hình 3)

Bộ chuyển đổi (Hình 2, Hình 3) ,

, (1) Bộ chuyển đổi tốc độ đơn

(1) Bộ chuyển đổi tốc độ đơn Nguyên tắc hoạt động của bộ chuyển đổi tốc độ đơn được trình bày trong hình 2, nguyên tắc được tóm tắt như sau:

Nguyên tắc hoạt động của bộ chuyển đổi tốc độ đơn được trình bày trong hình 2, nguyên tắc được tóm tắt như sau: Trong đó θlà góc đầu vào tương tự.

Trong đó θlà góc đầu vào tương tự. ,

, Hai tín hiệu được nhân với góc kỹ thuật số φ của lên / xuống bên trong

Hai tín hiệu được nhân với góc kỹ thuật số φ của lên / xuống bên trong .

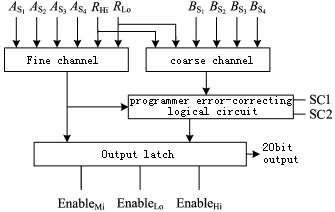

.Nguyên tắc hoạt động của bộ chuyển đổi 2 tốc độ được trình bày trong hình 3. Các | hoạt động của kênh thô và mịn của bộ chuyển đổi 2 tốc độ là |

|  |

| giống như tốc độ đơn đã đề cập ở trên, nhưng bộ chuyển đổi 2 tốc độ bao gồm hai bộ chuyển đổi tốc độ đơn và lôgic lỗi lập trình viên mạch điện. Kênh thô đáp ứng chuyển đổi từ góc logic 10 ~ 12bit | |

góc với góc kỹ thuật số. góc kỹ thuật số được chuyển đổi bởi kênh Coarse và | Kênh tốt được đưa vào lôgic sửa lỗi của lập trình viên | mạch tương ứng. Sau khi xử lý lỗi và sửa chữa, nó sẽ | xuất ra một chữ số nhị phân song song 20bit, được nhập vào đầu ra | chốt và đệm để đầu ra góc kỹ thuật số, hoàn thành toàn bộ | sự chuyển đổi. | |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 | Hình 2 Sơ đồ khối chức năng Hình 3 Sơ đồ khối chức năng bộ chuyển đổi tốc độ đơn của bộ chuyển đổi 2 tốc độ (3) Phương thức và thời gian truyền dữ liệu Đầu ra của bộ chuyển đổi 2 tốc độ dòng HTS20 đạt 20bit. Bởi vì và trong đó kiểm soát 3 trạng thái của chốt đầu ra, bộ chuyển đổi 2 tốc độ có thể dễ dàng kết nối với bus dữ liệu. và T1 T2 đều có giá trị ở mức thấp. EnableLo kiểm soát 8 bit thấp, EnableMi kiểm soát 8 bit giữa, EnableHi kiểm soát các bit cao còn lại. Dữ liệu của bộ chuyển đổi 2 tốc độ HTS20 được đọc như sau: Đặt thành logic “0”, sau 490μm, dữ liệu ở chốt 3 trạng thái của bộ chuyển đổi là được nâng cấp. Nó có thể đọc dữ liệu 8 bit thấp, 8 bit giữa và bit cao thông qua kiểm soát và Hình 4 Cung cấp thời gian đọc dữ liệu khi bộ chuyển đổi 2 tốc độ và bus dữ liệu 8 bit được kết nối. Để đảm bảo độ chính xác cao của bộ chuyển đổi 2 tốc độ, hãy chú ý những điều sau:

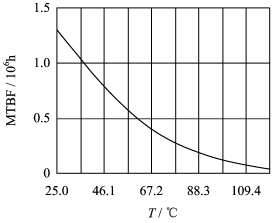

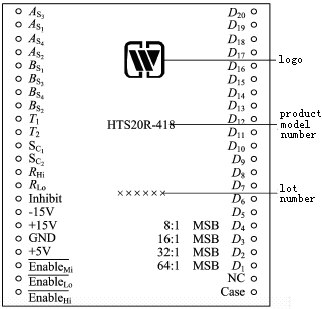

| Biên độ của tín hiệu đầu vào của các kênh thô và mịn phải được đảm bảo trong giá trị danh nghĩa 10%. Tần số của tín hiệu đầu vào và tín hiệu tham chiếu của kênh thô và kênh tinh phải là tần số hoạt động được chỉ định. Chuyển pha giữa tín hiệu đầu vào và tín hiệu tham chiếu thô kênh và pha giữa tín hiệu đầu vào và tín hiệu tham chiếu tốt kênh phải nhỏ hơn 10 °. Độ méo sóng của tín hiệu đầu vào và tín hiệu tham chiếu của kênh thô và kênh nhỏ phải nhỏ hơn 5%. Sự thay đổi của nguồn điện + 5V, ± 15V phải được đảm bảo trong khoảng ± 5%. 6 SƠ ĐỒ MTBF của Bộ chuyển đổi đồng bộ sang kỹ thuật số hoặc Bộ phân giải thành Bộ chuyển đổi kỹ thuật số Sê-ri HTS20 SDC / RDC 2 tốc độ có thể lập trình Bộ chuyển đổi (Hình 5) 7 CẤU HÌNH PIN của Bộ chuyển đổi từ đồng bộ sang kỹ thuật số hoặc Bộ phân giải thành Bộ chuyển đổi kỹ thuật số Sê-ri HTS20 SDC / RDC 2 tốc độ có thể lập trình Bộ chuyển đổi (Hình 6, Tab4) Hình 5 MTBF so với nhiệt độ Hình 6 Chốt ra hình chiếu từ trên xuống (Lưu ý: Theo GJB / Z 299B-98, giả sử mặt đất đó ở trong tình trạng tốt) Bảng 4 Mô tả chân Ghim Dễ nhớ Sự miêu tả Ghim Dễ nhớ Sự miêu tả As3 As1 As4 | 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 | As2 NC Bs1 Bs3 Bs4 Bs2 D5 D6 D7 D8 D9 SC1 SC2 RHi RLo Ức chế -15V + 15V GND + 5V Đầu vào kênh tốt Đầu vào kênh tốt | Đầu vào kênh tốt Đầu vào kênh tốt Đầu vào kênh thô Đầu vào kênh thô Đầu vào kênh thô Đầu vào kênh thô Chốt điều chỉnh để chuyển pha giữa tín hiệu và tham chiếu Chốt điều chỉnh để chuyển pha giữa tín hiệu và tham chiếu Chốt điều khiển chương trình cho thô và tỷ lệ tốc độ tốt Chốt điều khiển chương trình cho thô và tỷ lệ tốc độ tốt Chân đầu vào cho tham chiếu cao Chân đầu vào cho tham chiếu thấp Ngăn cản tín hiệu -15V đầu vào + Đầu vào 15V đất Đầu vào + 5V cho phép dữ liệu 8bits ở giữa | |

,

, D10

D10 D11

D11 D12

D12 D13

D13 D14

D14

Không kết nối Đầu ra của góc kỹ thuật số kết hợp cao nhất | Đầu ra của góc kỹ thuật số kết hợp | Đầu ra của góc kỹ thuật số kết hợp Đầu ra của góc kỹ thuật số kết hợp | Đầu ra của góc kỹ thuật số kết hợp | Đầu ra của góc kỹ thuật số kết hợp Đầu ra của góc kỹ thuật số kết hợp | Đầu ra của góc kỹ thuật số kết hợp |

Đầu ra của góc kỹ thuật số kết hợp | Đầu ra của góc kỹ thuật số kết hợp | 8 | Đầu ra của góc kỹ thuật số kết hợp | 15 | Đầu ra của góc kỹ thuật số kết hợp |

2 | Đầu ra của góc kỹ thuật số kết hợp | 9 | Đầu ra của góc kỹ thuật số kết hợp | 16 | Đầu ra của góc kỹ thuật số kết hợp |

3 | Đầu ra của góc kỹ thuật số kết hợp | 10 | Đầu ra của góc kỹ thuật số kết hợp | 17 | Đầu ra của góc kỹ thuật số kết hợp |

4 | Đầu ra của góc kỹ thuật số kết hợp | 11 | Đầu ra của góc kỹ thuật số kết hợp ít nhất | 18 | Ghi chú: |

5 | Chân 3,7 của HTS20S không được kết nối. | 12 | As1, As2, As3, As4 là đầu vào kênh tốt. Nếu đồng bộ hóa được trang bị ba dây, As4 không được sử dụng. | 19 | Bs1, Bs2, Bs3, Bs4 là đầu vào kênh thô. Nếu đồng bộ hóa được trang bị ba dây, Bs4 không được sử dụng. |

6 | RHi, RLo là đầu vào tín hiệu tham chiếu. | 13 | Ức chế là tín hiệu ức chế được kết nối với nguồn điện 5V bằng điện trở kéo lên. Khi Sự ức chế có giá trị lôgic “0”, bên trong sẽ bị ức chế. Sau 490ns, dữ liệu hợp lệ được xuất ra và có thể đọc được. Khi logic “1”, bộ chuyển đổi khôi phục trạng thái theo dõi, dữ liệu đầu ra là dữ liệu không hợp lệ. | 20 | Ức chế |

7 | và | 14 | là ba chân điều khiển trạng thái của đầu ra dữ liệu, xác định trạng thái |

Trường hợp là trường hợp pin.

D1 ~ D20 là Đầu ra của góc kỹ thuật số kết hợp. D20 là ít quan trọng nhất

chút. Khi tỷ lệ tốc độ là 1: 8, D4 là bit quan trọng nhất. Khi tốc độ | tỷ lệ là 1:16, D3 là bit quan trọng nhất. Khi tỷ lệ tốc độ là 1:32, D2 | là bit quan trọng nhất. Khi tỷ lệ tốc độ là 1:64, D1 là | bit đáng kể. BẢNG TRỌNG LƯỢNG 8 BIT của Bộ chuyển đổi hoặc Bộ phân giải từ đồng bộ sang kỹ thuật số | sang Bộ chuyển đổi kỹ thuật số Sê-ri HTS20 SDC hoặc RDC 2 tốc độ có thể lập trình Bộ chuyển đổi (Tab 5) | Bảng 5 Bảng khối lượng bit | Chút | con số Trọng lượng (độ) | Chút |

con số | Trọng lượng (độ) Chút | con số | Trọng lượng (độ) | 1 (MSB) | 180.0000 1.1063 | 0,011 (40 giây) | 90.0000 |

|

|

| 45.0000 |

X

X