Nguồn hoạt động sử dụng nguồn DC ± 15V và + 5V. Có hai loại tín hiệu đầu ra: tín hiệu tham chiếu và đồng bộ ba dòng (bộ chuyển đổi SDC) hoặc bộ phân giải bốn dòng và tín hiệu tham chiếu (bộ chuyển đổi RDC); đầu ra thông qua các mã kỹ thuật số song song của hệ thống nhị phân.

| Độ phân giải: 12 bit, 14 bit |  |

| Tốc độ theo dõi cao | |

| Tích hợp lai, vỏ kim loại | |

| Đầu ra chốt ba trạng thái | |

| Với tín hiệu vận tốc đầu ra Vel | |

| Khả năng tương thích vô thời hạn với dòng AD1740 |

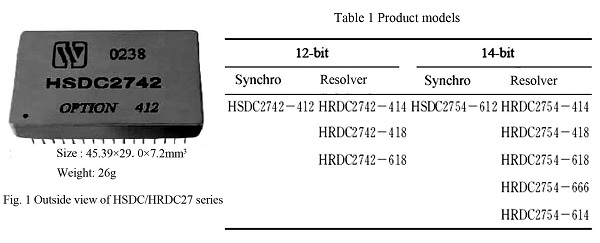

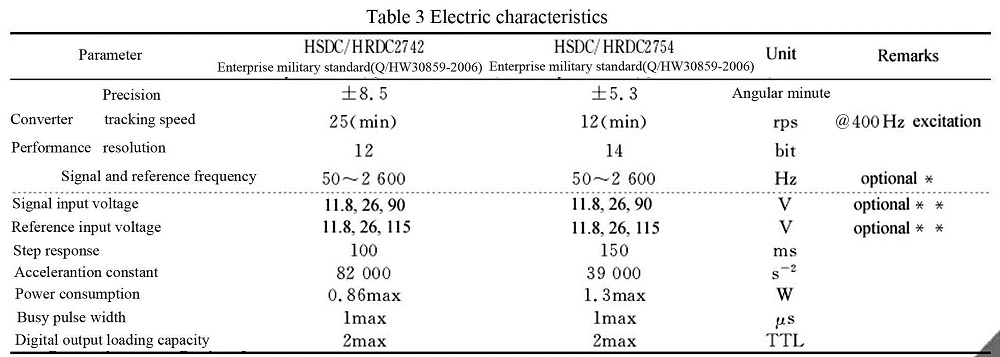

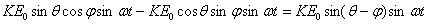

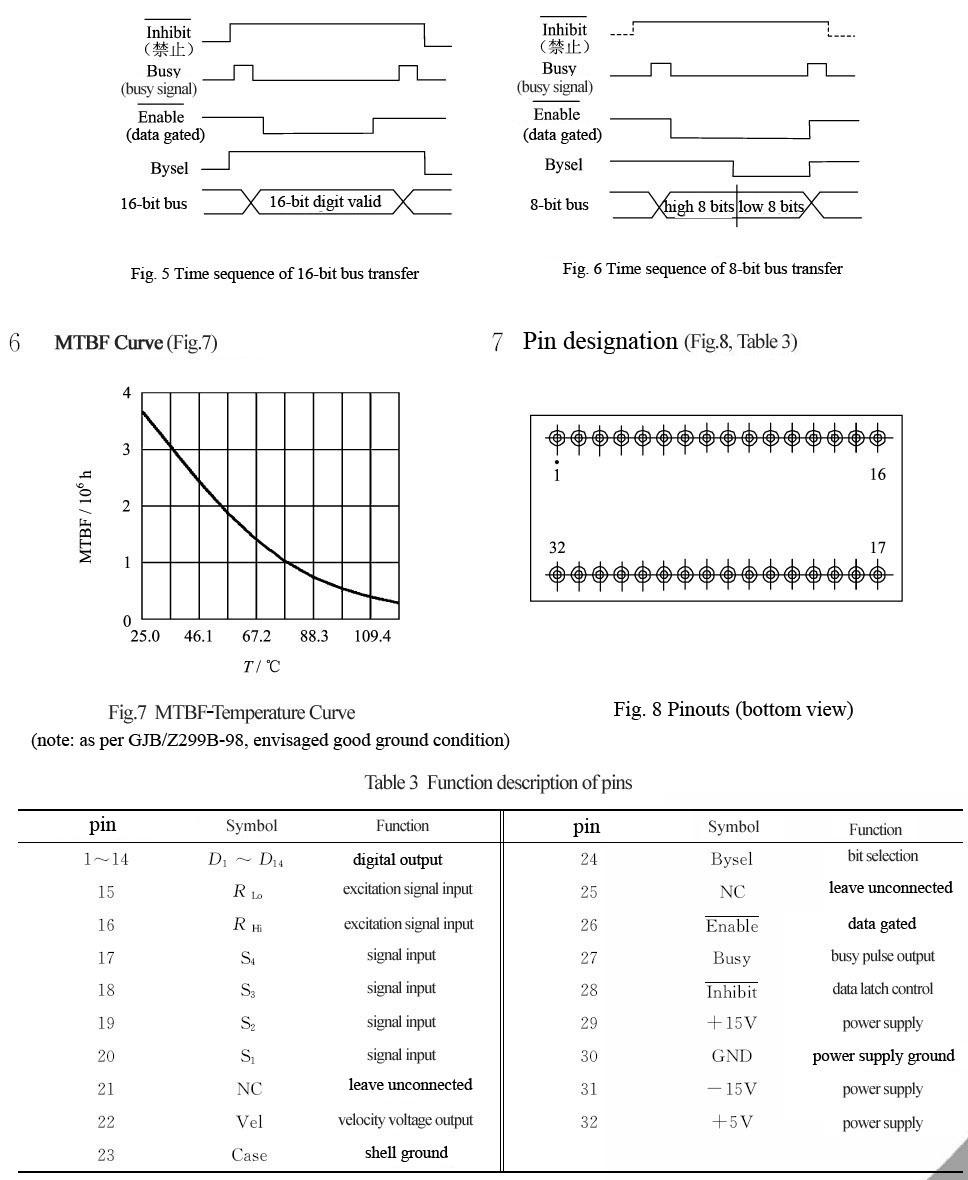

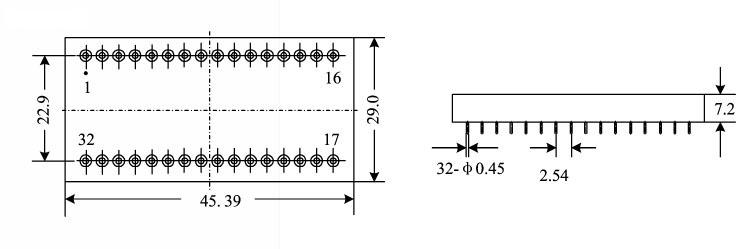

Sê-ri HSDC / HRDC27 là bộ chuyển đổi kỹ thuật số để đồng bộ hóa hoặc bộ phân giải thành bộ chuyển đổi kỹ thuật số để theo dõi liên tục vòng lặp servo loại II, nó chốt song song và xuất dữ liệu mã hóa nhị phân tự nhiên 12-bit hoặc 14-bit với kim loại kép trong dòng 32-bit gói, có ưu điểm là khối lượng nhỏ, trọng lượng nhẹ và độ tin cậy cao, v.v., nó được ứng dụng rộng rãi trong hệ thống điều khiển tự động như hệ thống Radar, hệ thống định vị, v.v.

Nguồn hoạt động sử dụng nguồn DC ± 15V và + 5V. Có hai loại tín hiệu đầu ra: tín hiệu tham chiếu và đồng bộ ba dòng (bộ chuyển đổi SDC) hoặc bộ phân giải bốn dòng và tín hiệu tham chiếu (bộ chuyển đổi RDC); đầu ra thông qua các mã kỹ thuật số song song của hệ thống nhị phân.

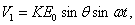

Bảng 2 Các điều kiện định mức và điều kiện vận hành khuyến nghị

Giá thầu tối đa tuyệt đối giá trị đánh giá | Điện áp cung cấp Vs: ± 17,5V |

Điện áp logic VL: + 5.5V | |

Phạm vi nhiệt độ lưu trữ: -55 ℃ ~ + 125 ℃ | |

Điều kiện hoạt động được đề xuất | Điện áp cung cấp Vs: ± 5V |

Điện áp logic VL: 5V | |

Giá trị hiệu dụng của điện áp tham chiếu VRef: ± 10% giá trị danh định | |

Giá trị của điện áp tín hiệu V1 *: ± 5% giá trị danh nghĩa | |

Tần số tham chiếu f *: 50Hz ~ 2.6kHz | |

Dải nhiệt độ hoạt động TA: -40 ~ + 85 ℃ , -55 ~ + 105 ℃ |

Lưu ý: * cho biết nó có thể được tùy chỉnh theo yêu cầu của người dùng.

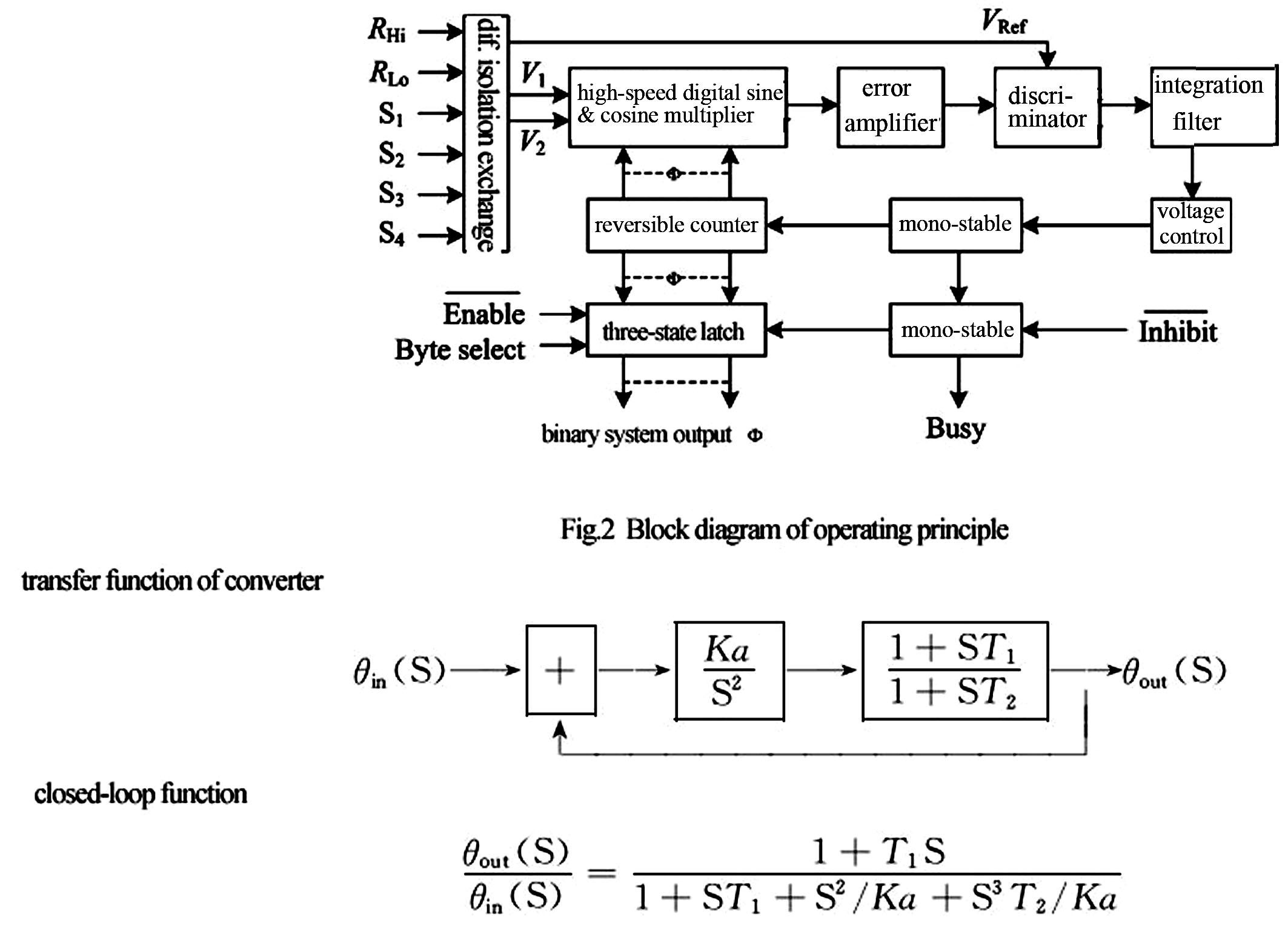

| đầu ra; đọc dữ liệu 12 bit hoặc 14 bit; đặt Ức chế thành lôgic “1” để |  |

| Truyền 16-bit). | B: bộ chuyển đổi được kết nối với bus 8 bit, bit D1 ~ D8 được kết nối với bus dữ liệu và phần còn lại trống. |

| |

| Ức chế là | |

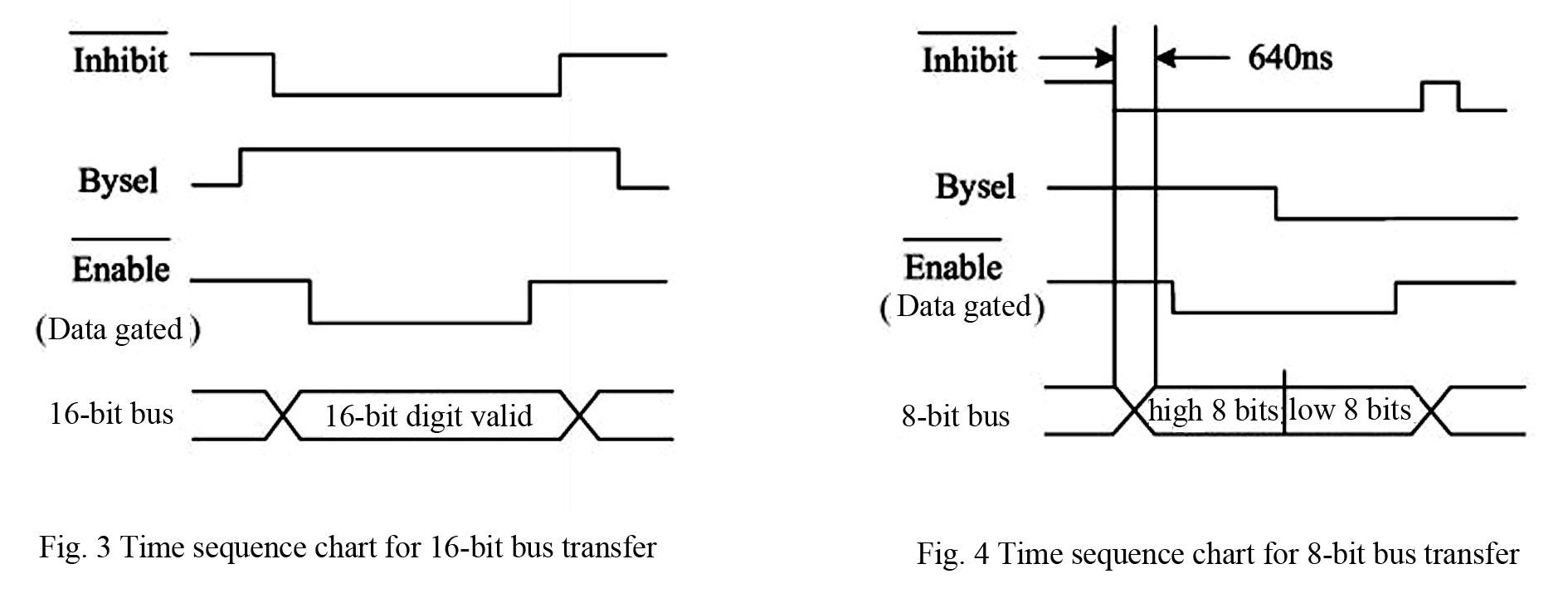

| Bật thành logic “0”, dữ liệu chốt bên trong bộ chuyển đổi được phép | được đầu ra; nếu Byse1 được đặt thành logic “1”, bộ chuyển đổi trực tiếp đọc | dữ liệu 8 bit cao hơn, nếu Byse1 được đặt thành logic “0”, bộ chuyển đổi sẽ đọc | các bit còn lại, tự động thêm số 0 cho các bit không đầy đủ; đặt điều khiển khóa dữ liệu Cấm (Tín hiệu cấm) thành logic “1” để sẵn sàng đọc dữ liệu hợp lệ tiếp theo (xem Hình 3 và Hình 4 cho chuỗi thời gian truyền 8 bit) | (2) Phương thức bận (đọc không đồng bộ): | Trong chế độ đọc không đồng bộ, điều khiển khóa dữ liệu cấm (Tín hiệu cấm) được đặt thành logic “1” hoặc trống, cho dù vòng lặp nội bộ luôn ở trong | trạng thái ổn định hoặc liệu dữ liệu đầu ra có hợp lệ hay không sẽ được xác định | thông qua trạng thái của tín hiệu bận rộn Bận. Khi tín hiệu Bận ở mức cao | , nó cho biết dữ liệu đang được chuyển đổi và dữ liệu tại |

| thời gian không ổn định và không hợp lệ; khi tín hiệu Bận ở mức thấp, nó | cho biết quá trình chuyển đổi dữ liệu đã được hoàn thành và dữ liệu tại | Au | thời gian ổn định và hợp lệ. Khi mức cao xảy ra trong Bận trong khi đọc, | Au | việc đọc thời gian này không hợp lệ. Ở chế độ đọc không đồng bộ, Bận | Au | đầu ra là tập xung của mức TTL, độ rộng giữa liên quan đến | tốc độ quay. Tương tự như vậy, cũng có hai sử dụng 8-bit và 16-bit |

X

X