| Chuyển đổi cách ly vi sai nội bộ |  |

| Độ phân giải: 16 bit | |

| Đầu ra chốt ba trạng thái | |

| Theo dõi không bị gián đoạn trong quá trình truyền dữ liệu | |

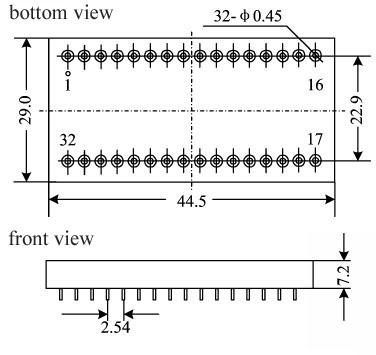

| Gói kim loại 32 dây |

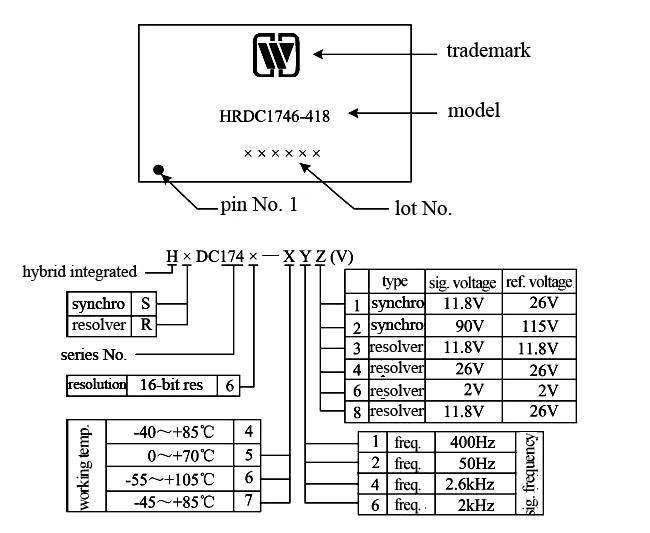

Bộ chuyển đổi đồng bộ / phân giải sê-ri HSDC / HRDC1746 sang bộ chuyển đổi kỹ thuật số được thiết kế | trên nguyên tắc của nguyên tắc theo dõi servo loại II và sử dụng | |||||

đầu vào cách ly vi sai, đầu ra dữ liệu thông qua chốt ba trạng thái | chế độ, nó phù hợp để chuyển đổi tín hiệu tương tự / tín hiệu kỹ thuật số của | đồng bộ ba dây và bộ phân giải bốn dây. Với tốc độ chuyển đổi nhanh chóng | và hiệu suất ổn định và đáng tin cậy, thiết bị này có thể được ứng dụng rộng rãi trong hệ thống đo góc và điều khiển tự động. | Sản phẩm này được tạo ra bởi quá trình tích hợp màng dày và được | ||

Gói kim loại kín hoàn toàn DIP 32 dây. Cả thiết kế và | ||||||

sản xuất sản phẩm đáp ứng các yêu cầu của GJB2438A-2002 | “Đặc điểm kỹ thuật chung cho mạch tích hợp lai” và cụ thể | thông số kỹ thuật của sản phẩm. | ||||

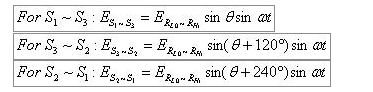

4. Hiệu suất điện (Bảng 2, Bảng 3) | Đồng bộ với Bộ chuyển đổi kỹ thuật số hoặc Bộ phân giải thành Bộ chuyển đổi kỹ thuật số (Sê-ri HSDC / HRDC1746) | Bảng 2 Các điều kiện định mức và điều kiện vận hành khuyến nghị | Bảng 3 Đặc điểm điện | Giá thầu tối đa tuyệt đối giá trị đánh giá | ||

Điện áp cung cấp Vs: ± 17,25VDC | Tham số | -3 | 3 | |||

HSDC / HRDC | Dòng 1746 | 16 | ||||

Ghi chú | Điện áp cung cấp logic VL: + 7V | 50 | Phạm vi nhiệt độ lưu trữ: -55 ℃ ~ 150 ℃ | |||

Tối thiểu. | Tối đa | 2 | 90 | |||

Điều kiện hoạt động được đề xuất | Điện áp cung cấp Vs: ± 15 ± 5% | 2 | Độ chính xác / phút góc | |||

| 2,6k |  |

| Độ lệch pha giữa tín hiệu và kích thích: < ± 10% Điện áp tín hiệu (giá trị hiệu dụng) / V Phạm vi nhiệt độ hoạt động (TA): -40 ~ + 105 ℃  | |

| Điện áp tham chiếu (giá trị hiệu dụng) / V | 115 |

| |

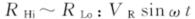

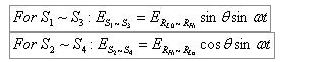

| một hàm lỗi thu được: |

Thông qua khuếch đại lỗi, phân biệt pha và lọcof hàm lỗi, sin (θ-φ) thu được, khi θ-φ u003d 0 (trong độ chính xác | của bộ chuyển đổi), lỗi này sẽ làm cho điện áp được kiểm soátofxung hiệu chỉnh đầu ra dao động để thay đổi góc kỹ thuật số nhị phân φ |

| |

| của bộ đếm thuận nghịch để làm cho giá trị φ đầu ra bằng | đầu vào θ trong độ chính xác của bộ chuyển đổi, hệ thống trở nên ổn định |

| và có thể theo dõi sự thay đổi của góc đầu vào φ. Theo cách này, một kỹ thuật số nhị phân | |

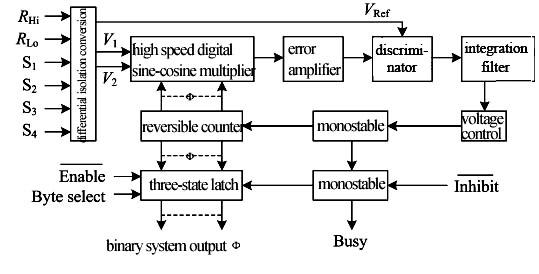

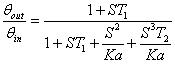

bộ đếm thuận nghịch (Hình 2). | Hình 2 Sơ đồ khối mạch | (1) Đặc điểm động | Chức năng truyền của bộ chuyển đổi được thể hiện trong Hình 3: | Tăng vòng lặp mở: | Chức năng vòng kín: |

1 | NC | Đối với mô-đun của mô hình này, Ka u003d 48000 / S2, T1 u003d 7,1ms, T2 u003d 1,25ms | 17 | NC | Hình 3 Chuyển chức năng của bộ chuyển đổi |

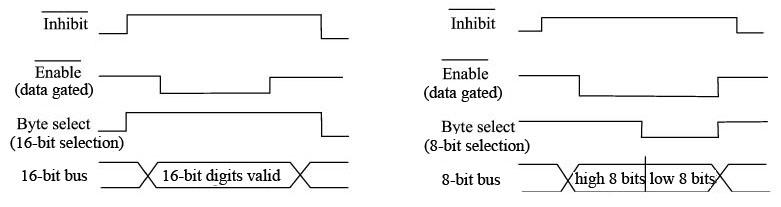

2 | D9 | (2) Phương thức truyền dữ liệu và trình tự thời gian | 18 | Kiểm soát chọn chip Bật | Chân này là chân đầu vào của logic điều khiển, chức năng của nó là đầu ra |

3 | dữ liệu đến bộ chuyển đổi để thực hiện điều khiển ba trạng thái. Mức độ thấp là | hợp lệ, dữ liệu đầu ra của bộ chuyển đổi chiếm bus dữ liệu. Khi nó ở | 19 | mức cao, chân đầu ra dữ liệu của bộ chuyển đổi ở ba trạng thái, | thiết bị không chiếm xe buýt. |

4 | Byte chọn | Chân này là chân đầu vào điều khiển, chức năng của nó là thực thi bên ngoài | 20 | kiểm soát lựa chọn trên dữ liệu đầu ra của bộ chuyển đổi trong quá trình truyền | chế độ của bus dữ liệu 8 bit hoặc bus dữ liệu 16 bit. Khi chuyển bus dữ liệu 16-bit |

5 | chế độ là bắt buộc, giữ cho chân logic này ở mức cao, dữ liệu sẽ | được chuyển trong bus, đầu ra byte cao ở chân D1 đến D8 (D1 là | 21 | bit cao) và byte thấp nằm trong D9 đến D16. Khi chuyển bus dữ liệu 8 bit | cần chế độ, dữ liệu thu được ở chân D1 đến D8 (được sắp xếp từ mức cao |

6 | xuống thấp), và 8 bit cao và 8 bit thấp thu được trong hai thời gian | trình tự, nói cách khác, khi Byte select là mức logic cao, 8 bit cao | 22 | là đầu ra và khi nó ở mức logic thấp, 8 bit thấp được xuất ra. | Điều khiển khóa dữ liệu (Tín hiệu cấm) |

7 | Chân này là chân đầu vào của logic điều khiển, chức năng của nó là đầu ra | dữ liệu từ bên ngoài đến bộ chuyển đổi để nhận ra chốt hoặc bỏ qua tùy chọn | 23 | điều khiển. Ở mức cao, dữ liệu đầu ra của bộ chuyển đổi trực tiếp | đầu ra mà không cần chốt, hãy xem biểu đồ trình tự thời gian của dữ liệu |

8 | chuyển khoản. Ở mức thấp, dữ liệu đầu ra của bộ chuyển đổi được chốt, | vòng lặp nội bộ không bị gián đoạn và theo dõi vẫn hoạt động | 24 | D1 | thời gian, nhưng bộ đếm không xuất dữ liệu. Khi nào cần chuyển |

9 | dữ liệu, trước tiên bộ chuyển đổi tạo ra tín hiệu điều khiển Ức chế để khóa dữ liệu từ cao xuống thấp, giữ mức logic ở mức thấp trong 640ns, sau đó đặt Kích hoạt đầu vào thành thấp (tại thời điểm này thiết bị chiếm bus dữ liệu), và sau đó | lấy dữ liệu thông qua Byte select, sau đó chuyển tất cả các lôgic điều khiển thành cao | 25 | D2 | để làm mới và chốt dữ liệu để sẵn sàng chuyển |

10 | dữ liệu tiếp theo, vui lòng tham khảo biểu đồ trình tự thời gian của truyền dữ liệu Hình 4 | và Hình 5. | 26 | D3 | (3) Phương pháp suy giảm của tín hiệu đầu vào (Hình 4 và Hình 5) |

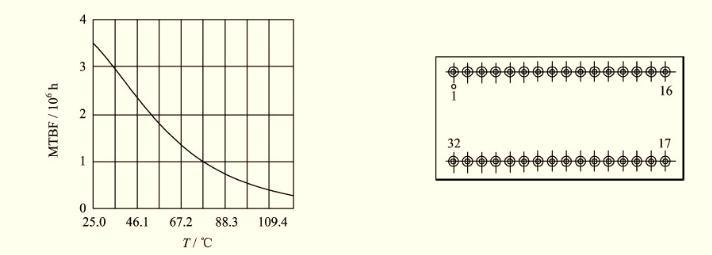

11 | Hình 4 Chuỗi thời gian của truyền bus 16 bit | Hình 5 Chuỗi thời gian của truyền bus 8 bit | 27 | D4 | 6. Đường cong MTBF (Hình 6) |

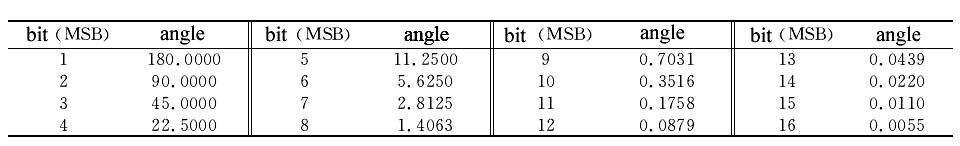

12 | Đồng bộ với Bộ chuyển đổi kỹ thuật số hoặc Bộ phân giải thành Bộ chuyển đổi kỹ thuật số (Sê-ri HSDC / HRDC1746) | 7. Ký hiệu chân (Hình 7, Bảng 4) | 28 | D5 | Đồng bộ với Bộ chuyển đổi kỹ thuật số hoặc Bộ phân giải thành Bộ chuyển đổi kỹ thuật số (Sê-ri HSDC / HRDC1746) |

13 | S3 | Hình 6 Đường cong nhiệt độ MTBF | 29 | D6 | Hình 7 Chỉ định chân (Hình dưới) |

14 | S2 | (Lưu ý: theo GJB / Z299B-98, dự kiến tình trạng mặt đất tốt) | 30 | D7 | Bảng 4 Mô tả chức năng của các đầu nối dây dẫn |

15 | S1 | Ghim | 31 | D7 | Biểu tượng |

16 | NC | Nghĩa | 32 | NC | Ghim |

Đất | D12 | Đầu ra kỹ thuật số cho 12bit | -VS | -15V cung cấp điện | D13 | Đầu ra kỹ thuật số cho 13bit | + VS | + Nguồn điện 15V |

D14 | Đầu ra kỹ thuật số cho 14bit | Ni | Ức chế | Ni | Kiểm soát khóa dữ liệu | D15 | Đầu ra kỹ thuật số cho 15bit |

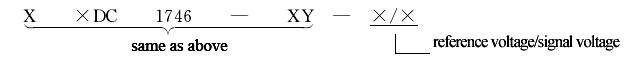

X

X